Join the Upcoming Seminar on Chiplet Implementation and Testing Techniques

Upcoming Seminar on Chiplet Implementation and Testing Techniques

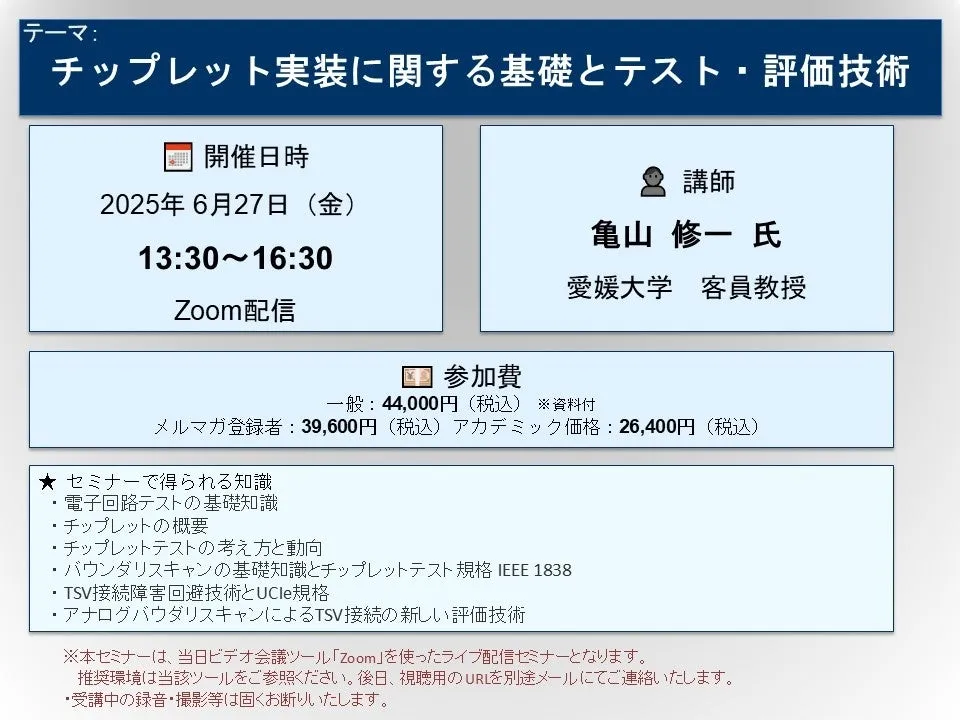

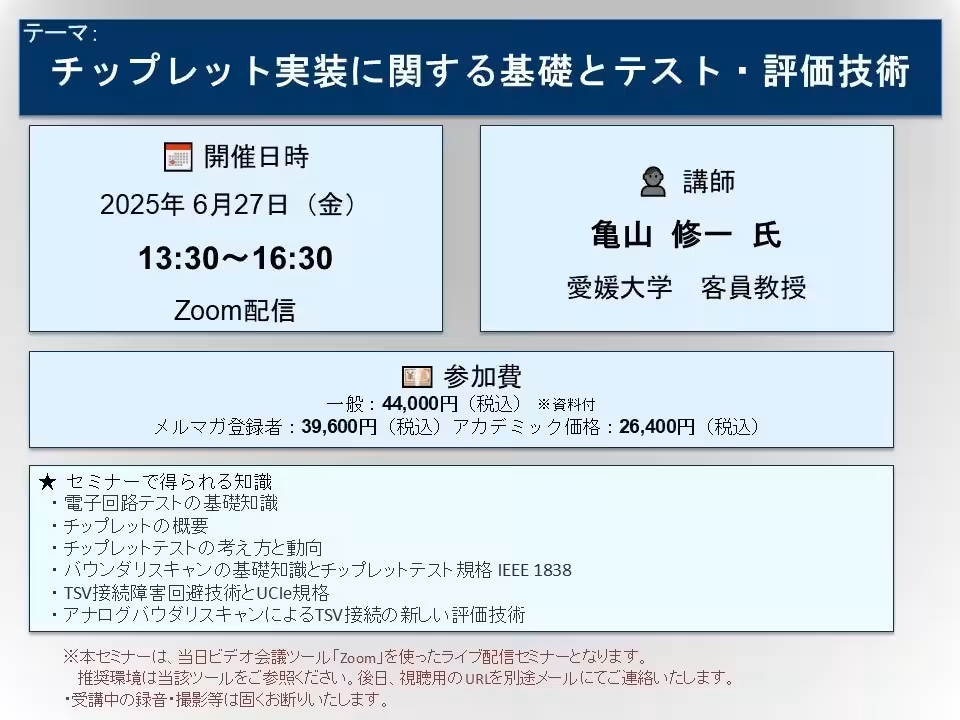

On June 27, 2025, from 13:30 to 16:30, CMC Research will host a pivotal live streaming seminar on chiplet implementation and testing techniques via Zoom. This seminar will provide essential insights into the evolving world of electronic circuit testing and chiplet technology.

Seminar Details

The seminar titled, "Fundamentals of Chiplet Implementation and Testing Techniques," will feature Shuuichi Kameyama, a visiting professor at Ehime University. The participation fee is set at 44,000 JPY (including tax), with discounts for newsletter subscribers at 39,600 JPY and an academic price of 26,400 JPY (also including tax). Attendees will receive relevant materials as part of their fee.

Key Topics Covered

Participants will gain knowledge in various areas during the seminar:

- - Fundamentals of electronic circuit testing

- - Overview of chiplets

- - Testing considerations and trends for chiplets

- - Boundary scan basics and IEEE 1838 standards for chiplet testing

- - Techniques for avoiding TSV connection failures and understanding the UCIe standard

- - New evaluation techniques for TSV connections via analog boundary scan

Target Audience

This seminar is designed for anyone interested in chiplet implementation and testing, making it ideal for professionals looking to deepen their understanding of these advanced topics.

Agenda Overview

1. Introduction

- Speaker introduction

- Technology and test techniques for large-scale Fujitsu computers

- Deployment of boundary scan technology

2. Overview of Chiplets

- What are chiplets?

- The reasons for the current significance of chiplets

- Moore’s Law and scaling principles

- Effects and applications of chiplets

- Examples of chiplet implementations and trends in interposers

3. Trends in Chiplet Testing

- Testing flow for integrated chiplets

- Significance of Known Good Die (KGD)

- Challenges and strategies in wafer probe testing

- System-level testing implications

4. Interconnection Testing between Chiplets

- Manufacturing process for chiplet implementation boards

- Functionality testing and structural assessments

- Boundary scan fundamentals and IEEE 1149.1 tests

5. TSV Connection Quality Assessment Techniques

- Common defects in TSV connections and hybrid bonding challenges

- Importance of outlier detection in TSV evaluation

6. Q&A Session

Seminar Format

This seminar will take place as a live-streaming event through the Zoom platform, and recommended technical requirements for participation will be shared. Additionally, participants are requested not to record or photograph the session.

Registration

To register for the seminar, visit the CMC Research seminar website to sign up, and you will receive a separate email with the viewing link. Don't miss this opportunity to enhance your knowledge and skills in a critical area of technology.

For more information about the seminar or to explore future webinars scheduled by CMC Research, visit the official website: CMC Research

Join us for a deep dive into the world of chiplets and electronic testing—secure your spot now!

Topics Consumer Technology)

【About Using Articles】

You can freely use the title and article content by linking to the page where the article is posted.

※ Images cannot be used.

【About Links】

Links are free to use.